CSCI 210: Lab 7

Four

Bit Counter

Due:

9:59

PM

on

Monday,

November

14th

Preliminaries

We will be using circuitverse.org for this assignment. To start the assignment, click on your name on the upper righthand side of the website. Go to “My Groups” and then select the group for this class and you should see “Lab 7” under assignments. Click the “Start Working” button to start the assignment. After you click “Start Working” you can click “Launch Simulator” to start creating the assignment.

Assignment

In this lab, you will

- Build a clocked S-R latch

- Build a J-K flipflop out of S-R latches

- Build an four-bit counter out of J-K flipflops

Clocked S-R Latch

You should first build a clocked S-R Latch as a subcircuit. Lectures 19 and 20, as well as section 3.7 of the Zybook should be helpful to you here. The S-R latch must be a subcircuit to get full credit for the lab.

Your subcircuit should take in inputs S, R and C (for clock), and have outputs Q and Not Q. When C is 1, the outputs Q and Not Q are controlled by S and R. When C is 0, the outputs should not change regardless of the values of S and R. (Note that for this subcircuit, you should make the clock an input value, and not actually hook up the clock to the circuit.)

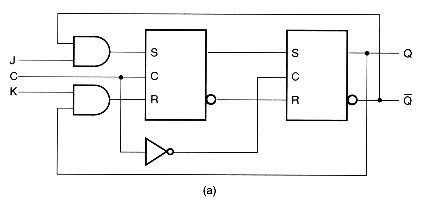

JK FlipFlop

Next you will build a JK Flipflop out of two clocked S-R latches. Your subcircuit inputs should be J, K and C (for clock again), and your output should be Q. The JK FlipFlop must be a subcircuit in order to get full credit for the lab. Below is a circuit diagram for a JK FlipFlop.

4-Bit Counter

Your main circuit is a four-bit counter which you will build out of four J-K flip-flops.

This circuit should not require any input from the user/viewer of the circuit; you should use the clock as input, and it should automatically make your counter increase by one for every clock cycle. Your output should be a binary number displaying the current count. You can either display this as 4 individual 1-bit outputs, or 1 four-bit output. Your counter should count through 0000, 0001, 0010, 0011,. . . , 1110, 1111 and then start over at 0000.

Let’s start by considering a 1-bit counter. Every clock cycle, the output should alternate between 0 and 1. See the timing diagram below. Notice how output X0 alternates between 0 and 1 and it stays at each of those for an entire clock period (the interval between the blue lines).

Look at Problem Set 8. There is a particular configuration of inputs to a J-K flip-flop that causes the output to “toggle” between 0 and 1 every time its clock input, C, changes from 1 to 0. Using a single J-K flip-flop, you can construct a 1-bit counter.

Next, let’s build a 2-bit counter. This should count as 00, 01, 10, 11, 00. Notice that the least-significant bit, X0, toggles on every clock cycle but X1 only toggles when X0 changes from a 1 to a 0, not when the clock changes from a 1 to a 0. In the image below, the blue vertical lines correspond to the counter values 00, 01, 10, 10, 11, 00, from left to right.

To get a 2-bit counter, we just need two J-K flip-flops with appropriate J and K values and with the clock input of the second J-K flip-flop being the output from the first flip-flop.

Similarly, we can build a 3-bit counter by adding another flip-flop. Look at the timing diagram below. When does X2 toggle?

We can continue this process to get a 4-bit counter.

Implementation Plan

You are required to build this counter using only with basic logic gates (i.e., AND, OR, NOT, NOR, NAND and XOR). You are not allowed to use the CircuitVerse latches and flip-flops. You should take the following steps:

- Build an S-R latch as a subcircuit;

- Build a J-K flip-flop as a subcircuit; and

- Build a four-bit counter out of four J-K flip-flops.

You are required to have a separate S-R latch and J-K flip-flop subcircuits to get full credit for the lab. You must build your own J-K flip-flops and S-R latches. Using the CircuitVerse latches of flip-flops will result in a failing grade for this lab.

Submission

Make sure to select the “save online” button to save your project. This will make your project available to us for grading.

C. Taylor, S. Checkoway